A question has bothered a lot, when I using "Vsource" which is from 'rfLib' library to run an ACPR, but I don't know how to set the element value of 'vsource', my question is how to get a help document about the elements in the rfLib library

how to get the physical model or model description of an element?

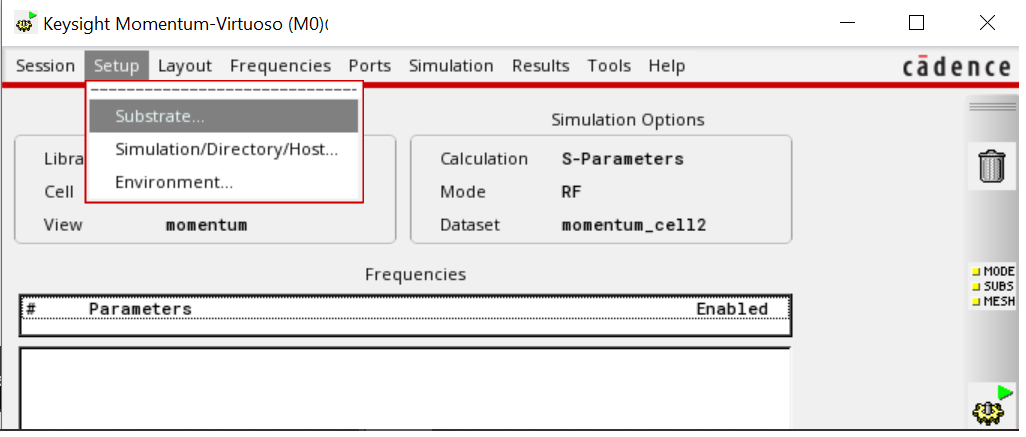

substrate layer of inductor

Hello, I have build an inductor as shown bellow, there are two layers layer 9 and layer 8 with a VIA connecting between them.

There are 3 layers where a substrate could be define.under layer 9, between layer 9 and layer 8 and above layer 8.

The only option i have is to load a file , but can i define it manualy some how?

Thanks

s-param ports problem in Goldengate s-param simulation

Hello, i am trying to simulate my inductor s-param with goldengate . i have built the schematics and defined the simulation as shown bellow.

but it says that i havent defined sparam ports although i did defined them in schematics .

i have added the error and the full log bellow.

i know that goldengate is a keysight product but my error is in the schematics step.

if still its beyong the scope i will try with spectre.

Thanks.

Executing: mccontrol inductor4_tst_SP.gg -ggparser -no_parallel -m amap -A ../psf -sim_output_file work -O 2 -o inductor4_tst_SP.gg.expanded.gg -I /projects/VLSI_labs/RFIC/yafimv/RF_090 -I .

mccontrol GoldenGate-2017-Update-0.2 (Tue 2018/10/16 17:22:09 UTC) (C) Keysight Technologies 2007-2018

Control program with pid 32113 started at 'Fri Jan 18 16:54:24 2019'.

ggparser GoldenGate-2017-Update-0.2 (Tue 2018/10/16 17:22:09 UTC) (C) Keysight Technologies 2007-2018

Parser started at Fri Jan 18 16:54:26 2019 (PID=32121).

Checking out a bundle license (will retry for up to one hour).

Bundle license check out time: 0.0348601 second(s).

Checking out a parser license (will retry for up to one hour).

Parser license check out time: 0.0184572 second(s).

Output cache directory: /a/home/cc/students/enginer/yafimv/.xpedion/cache/ahdl/

Parsing complete: 0s 244.867M.

Opened SimKit library libgg_elib_simkit_5_0.so.

Pre-elaboration complete: 0s 296.391M.

Elaborating...

Elaboration complete: 0s 296.391M.

Equation solve complete: 0s 296.391M.

Post-processing complete: 0s.

Print complete: 0s.

Execution complete: 1s 296.391M.

Total CPU Time : 1s.

/eda_disk/Keysight/GoldenGate-2017-Update-0.2/linux_x86_64/bin/ggsim: Successful parse.

##############################################################################

Executing: mccontrol inductor4_tst_SP.gg.expanded.gg -I /projects/VLSI_labs/RFIC/yafimv/RF_090 -I . -format ds -output_dir ../psf -output_data_dir . -warning inductor4_tst_SP.warning.log -error inductor4_tst_SP.error.log -no_parallel -liana

mccontrol GoldenGate-2017-Update-0.2 (Tue 2018/10/16 17:22:09 UTC) (C) Keysight Technologies 2007-2018

Control program with pid 32102 started at 'Fri Jan 18 16:54:31 2019'.

EEsof License Tools (*) Ver: 2018.04 Date: May 02,2018 Build: 108

GoldenGate (release ver. GoldenGate-2017-Update-0.2 build 6498 -- Oct 16 2018) (C) Keysight Technologies 2007-2018

Checking out a bundle license (will retry for up to one hour).

Bundle license check out time: 0.0524719 second(s).

Checking out a simulator license (will retry for up to one hour).

Simulator license check out time: 0.0173888 second(s).

Simulation 'at Fri Jan 18 16:54:34 2019, host micron.eng.tau.ac.il, process #32154'.

Total available memory : 31Gb, free: 10Gb

Current directory : '/data.cc/data/a/home/cc/students/enginer/yafimv/simulation/inductor4_tst/GoldenGate/schematic/netlist'.

GoldenGate binary : '/eda_disk/Keysight/GoldenGate-2017-Update-0.2/linux_x86_64/bin/liana_bin'

Argument list : 'inductor4_tst_SP.gg.expanded.gg -format ds -warning inductor4_tst_SP.warning.log -error inductor4_tst_SP.error.log -output_dir ../psf

-output_data_dir . -I /projects/VLSI_labs/RFIC/yafimv/RF_090 -I . '

main netlist file : inductor4_tst_SP.gg.expanded.gg.

Output directory : '/data.cc/data/a/home/cc/students/enginer/yafimv/simulation/inductor4_tst/GoldenGate/schematic/netlist/../psf'.

Output data directory : '.'.

Input data directory : '.'.

> Registry file list:

/eda_disk/Keysight/GoldenGate-2017-Update-0.2/etc/goldengate.conf

-------------------------------------------------------------------------------

* Exporting the following environment variables:

export GG_NETLIST_DIR = /data.cc/data/a/home/cc/students/enginer/yafimv/simulation/inductor4_tst/GoldenGate/schematic/netlist

export GG_IN_DATA = .

export GG_OUT_DATA = .

export GG_OUT_DIR = /data.cc/data/a/home/cc/students/enginer/yafimv/simulation/inductor4_tst/GoldenGate/schematic/netlist/../psf

* GoldenGate related environment variables values:

HOME = /a/home/cc/students/enginer/yafimv

XPEDION_DOT_DIR = /a/home/cc/students/enginer/yafimv/.xpedion

HPEESOF_DIR = /eda_disk/agilent/ADS2017

LD_LIBRARY_PATH = '/ahdl:/a/home/cc/students/enginer/yafimv/.xpedion/cache/ahdl:/eda_disk/Keysight/GoldenGate-2017-Update-0.2/linux_x86_64/lib64:/eda_disk/Keysight/GoldenGate-2017-Update-0.2/linux_x86_64/lib:/eda_disk/Keysight/GoldenGate-2017-Update-0.2/linux_x86_64/lib/32:/eda_disk/cadence/tools/IC/617_712/tools/lib:/eda_disk/cadence/tools/IC/617_712/share/oa/lib/linux_rhel50_gcc48x_64/opt:/eda_disk/cadence/tools/IC/617_712/tools.lnx86/Qt/64bit/lib:/eda_disk/cadence/tools/IC/617_712/tools.lnx86/dfII/lib/64bit:/eda_disk/cadence/tools/IC/617_712/tools.lnx86/sev/lib/64bit:/eda_disk/cadence/tools/IC/617_712/tools.lnx86/lib/64bit:/eda_disk/cadence/tools/IC/617_712/tools.lnx86/lib:/eda_disk/cadence/tools/IC/617_712/tools.lnx86/hdf5/lib/64bit:/eda_disk/cadence/tools/IC/617_712/tools.lnx86/lz4/lib/64bit:/eda_disk/cadence/tools/INCISIV/11.1/tools.lnx86/lib/64bit:/eda_disk/agilent/ADS2017/lib/linux_x86:/eda_disk/agilent/ADS2017/adsptolemy/lib.linux_x86:/eda_disk/agilent/ADS2017/lib/linux_x86_64:/eda_disk/agilent/ADS2017/adsptolemy/lib.linux_x86_64'

* Registry values:

Write Cache dir = $XPEDION_DOT_DIR/cache

-------------------------------------------------------------------------------

Reading file : 'inductor4_tst_SP.gg.expanded.gg' ( 0.00Mb).

Netlist reading time : 00:00.

-------------------------- Expanded Netlist Partlist --------------------------

port 2

snport 1

ccvns 1

total 4

-------------------------------------------------------------------------------

Expanding project file : 'inductor4_tst_SP'.

Expanding description...

Starting spare search...

...Finished spare search

** There are 0 spare nodes and 0 spare elements.

Cpu time for spare search: 00:00 ( 0.00 sec).

Expanding library elements...

Netlist expansion time : 00:00.

Using library hbsrc : (v. GoldenGate-2017-Update-0.2, Oct 16 2018, 11:44:11).

Performing kernel setup...

Random seed was set to 30105. It affects ET sources and internal functions. It does not affect statistical variables and Monte-Carlo simulation.

Circuit temperature : 27.00 C.

Nominal temperature : 27.00 C.

Element 'I0': Reading S-Parameter file : '/projects/inductor4/mommdl/text.txt'

------------------------ Internal GoldenGate Inventory ------------------------

external nodes 4

nodal matrix size 12

#netlist variables 37

#netlist equations 0

#non linear models 2

#non linear sources 0

Element part list:

* Internal instances:

base snport 1

base ccvns 1

base dspgv 2

total 4

* Library instances:

hbsrc port 2

total 2

Model part list:

spectre sine 2

total 2

-------------------------------------------------------------------------------

Circuit Signature '8e6b6be0e793eda1af7b8255e954dae3'.

-------------------------------------------------------------------------------

-------------------------------------------------------------------------------

Elapsed time : cpu: 00:00 ( 0.04 sec), wall clock: 00:00 ( 0.17 sec).

Using multithread simulation. Number of threads = 4.

Performing 'nominal' task.

Error: SP: No S-port defined. [119.72]

Elapsed time : cpu: 00:00 ( 0.05 sec), wall clock: 00:02 ( 2.59 sec).

Writing data set file '/data.cc/data/a/home/cc/simulation/inductor4_tst/GoldenGate/schematic/netlist/../psf/inductor4_tst_SP.ds'.

Elapsed time : cpu: 00:00 ( 0.06 sec), wall clock: 00:03 ( 3.83 sec).

Total memory : 45.195M.

Simulation completed on 'Fri Jan 18 16:54:38 2019'.

Fatals: 0, Errors: 1, Warnings: 0 (0 suppressed)

harmonic balance of oscilator spur injection

Hello, i have an oscilator oscilating at 10GHz, in theory if we add another VSIN source to the bias as shown bellow (18GHz) then those two spurs can bacome one spurunder certaing condtion,or at least both of them will show in the spectral plot.

i tried to see the 10GHz and 18GHz spur and to play with the added VSIN(defined as shown bellow) source to see this fenomena.

HB simulation was defined as two tones and HBNOISE as relative harmonics 2(because it says to do so in the error i got) .(as shown bellow)

how ever even when i changed the HBNOISE it didnt run, giving me the same error as shown bellow.

When i tried one tone HB then it ran but in the log i got and error regrding my VSIN source as shown bellow,the full log is shown in the end.

where did i go wrong shown these two spurs?

Thanks

Warning from spectre.

WARNING (SPECTRE-16707): Only tran supports psfxl format, result of other analyses will be in psfbin format.

Error found by spectre during periodic steady state analysis `hb'.

ERROR (CMI-2208): `V3' is a periodic input signal, which is inconsistent with autonomous circuits.

Analysis `hb' was terminated prematurely due to an error.

Error found by spectre.

ERROR (SPCRTRF-15225): The hbnoise analysis was skipped because a HB analysis must be run first.

************************************

Cadence (R) Virtuoso (R) Spectre (R) Circuit Simulator

Version 15.1.0.801.isr17 64bit -- 19 Apr 2017

Copyright (C) 1989-2017 Cadence Design Systems, Inc. All rights reserved worldwide. Cadence, Virtuoso and Spectre are registered trademarks of Cadence Design Systems, Inc. All others are the property of their respective holders.

Includes RSA BSAFE(R) Cryptographic or Security Protocol Software from RSA Security, Inc.

User: yafimv Host: micron.eng.tau.ac.il HostID: 428454C2 PID: 28402

Memory available: 239.1490 MB physical: 33.6702 GB

Linux : Red Hat Enterprise Linux Server release 6.9 (Santiago)

CPU Type: Intel(R) Xeon(R) CPU E5420 @ 2.50GHz

All processors running at 1998.0 MHz

Socket: Processors

0: 0, 2, 4, 6

1: 1, 3, 5, 7

System load averages (1min, 5min, 15min) : 20.8 %, 13.6 %, 7.9 %

Simulating `input.scs' on micron.eng.tau.ac.il at 11:47:26 AM, Sat Jan 19, 2019 (process id: 28402).

Current working directory: /data.cc/data/a/home/cc/students/enginer/yafimv/simulation/ex3_divider/spectre/schematic/netlist

Command line:

/eda_disk/cadence/tools/MMSIM/151/tools/bin/spectre -64 input.scs \

+escchars +log ../psf/spectre.out +inter=mpsc \

+mpssession=spectre0_21767_1 -format psfxl -raw ../psf \

+lqtimeout 900 -maxw 5 -maxn 5

spectre pid = 28402

Loading /eda_disk/cadence/tools/MMSIM/151/tools.lnx86/cmi/lib/64bit/5.0/libinfineon_sh.so ...

Loading /eda_disk/cadence/tools/MMSIM/151/tools.lnx86/cmi/lib/64bit/5.0/libphilips_o_sh.so ...

Loading /eda_disk/cadence/tools/MMSIM/151/tools.lnx86/cmi/lib/64bit/5.0/libphilips_sh.so ...

Loading /eda_disk/cadence/tools/MMSIM/151/tools.lnx86/cmi/lib/64bit/5.0/libsparam_sh.so ...

Loading /eda_disk/cadence/tools/MMSIM/151/tools.lnx86/cmi/lib/64bit/5.0/libstmodels_sh.so ...

Reading file: /data.cc/data/a/home/cc/students/enginer/yafimv/simulation/ex3_divider/spectre/schematic/netlist/input.scs

Reading file: /eda_disk/cadence/tools/MMSIM/151/tools.lnx86/spectre/etc/configs/spectre.cfg

Reading file: /eda_disk/cadence/tools/MMSIM/151/tools.lnx86/spectre/etc/configs/mapsubckt.cfg

Reading file: /eda_disk/pdks/UMC/UMC90nm/Models/Spectre/L90_25IO_NVT_V021.lib.scs

Reading file: /eda_disk/pdks/UMC/UMC90nm/Models/Spectre/L90_25IO_NVT_V021.mdl.scs

Reading file: /eda_disk/pdks/UMC/UMC90nm/Models/Spectre/L90_25IO_V111.lib.scs

Reading file: /eda_disk/pdks/UMC/UMC90nm/Models/Spectre/L90_25IO_V111.mdl.scs

Reading file: /eda_disk/pdks/UMC/UMC90nm/Models/Spectre/L90_NCAP25_V113.lib.scs

Reading file: /eda_disk/pdks/UMC/UMC90nm/Models/Spectre/L90_NCAP25_V113.mdl.scs

Reading file: /eda_disk/pdks/UMC/UMC90nm/Models/Spectre/L90_varmis_25_rf_V011.lib.scs

Reading file: /eda_disk/pdks/UMC/UMC90nm/Models/Spectre/L90_varmis_25_rf_V011.mdl.scs

Reading file: /eda_disk/pdks/UMC/UMC90nm/Models/Spectre/L90_33IO_GOX52_VT21.lib.scs

Reading file: /eda_disk/pdks/UMC/UMC90nm/Models/Spectre/L90_33IO_GOX52_VT21.mdl.scs

Reading file: /eda_disk/pdks/UMC/UMC90nm/Models/Spectre/L90_25IO_RF_V021.lib.scs

Reading file: /eda_disk/pdks/UMC/UMC90nm/Models/Spectre/L90_25IO_RF_V021.mdl.scs

Reading file: /eda_disk/pdks/UMC/UMC90nm/Models/Spectre/L90-resistor-control-V041.scs

Reading file: /eda_disk/pdks/UMC/UMC90nm/Models/Spectre/L90_res.va

Reading link: /eda_disk/cadence/tools/MMSIM/151/tools.lnx86/spectre/etc/ahdl/constants.h

Reading file: /eda_disk/cadence/tools/MMSIM/151/tools.lnx86/spectre/etc/ahdl/constants.vams

Reading link: /eda_disk/cadence/tools/MMSIM/151/tools.lnx86/spectre/etc/ahdl/discipline.h

Reading file: /eda_disk/cadence/tools/MMSIM/151/tools.lnx86/spectre/etc/ahdl/disciplines.vams

Reading file: /eda_disk/pdks/UMC/UMC90nm/Models/Spectre/L90_r_ppo_V031.lib.scs

Reading file: /eda_disk/pdks/UMC/UMC90nm/Models/Spectre/L90_r_ppo_V031.mdl.scs

Reading file: /eda_disk/pdks/UMC/UMC90nm/Models/Spectre/L90_r_npo_V031.lib.scs

Reading file: /eda_disk/pdks/UMC/UMC90nm/Models/Spectre/L90_r_npo_V031.mdl.scs

Reading file: /eda_disk/pdks/UMC/UMC90nm/Models/Spectre/L90_rnhr_V031.lib.scs

Reading file: /eda_disk/pdks/UMC/UMC90nm/Models/Spectre/L90_rnhr_V031.mdl.scs

Reading file: /eda_disk/pdks/UMC/UMC90nm/Models/Spectre/L90_rsnwell_V031.lib.scs

Reading file: /eda_disk/pdks/UMC/UMC90nm/Models/Spectre/L90_rsnwell_V031.mdl.scs

Reading file: /eda_disk/pdks/UMC/UMC90nm/Models/Spectre/L90_r_nd_V031.lib.scs

Reading file: /eda_disk/pdks/UMC/UMC90nm/Models/Spectre/L90_r_nd_V031.mdl.scs

Reading file: /eda_disk/pdks/UMC/UMC90nm/Models/Spectre/L90_r_pd_V031.lib.scs

Reading file: /eda_disk/pdks/UMC/UMC90nm/Models/Spectre/L90_r_pd_V031.mdl.scs

Reading file: /eda_disk/pdks/UMC/UMC90nm/Models/Spectre/L90_r_metal_V011.lib.scs

Reading file: /eda_disk/pdks/UMC/UMC90nm/Models/Spectre/L90_r_metal_V011.mdl.scs

Reading file: /eda_disk/pdks/UMC/UMC90nm/Models/Spectre/L90_BJT_V111.lib.scs

Reading file: /eda_disk/pdks/UMC/UMC90nm/Models/Spectre/L90_BJT_V111.mdl.scs

Reading file: /eda_disk/pdks/UMC/UMC90nm/Models/Spectre/L90_DIODE_V101.mdl.scs

Reading file: /eda_disk/pdks/UMC/UMC90nm/Models/Spectre/L90_LL12_RF_V021.lib.scs

Reading file: /eda_disk/pdks/UMC/UMC90nm/Models/Spectre/L90_LL12_RF_V021.mdl.scs

Reading file: /eda_disk/pdks/UMC/UMC90nm/Models/Spectre/L90_LLLVT12_RF_VTAB.lib.scs

Reading file: /eda_disk/pdks/UMC/UMC90nm/Models/Spectre/L90_LLLVT12_RF_VTAB.mdl.scs

Reading file: /eda_disk/pdks/UMC/UMC90nm/Models/Spectre/L90_LL12_V102.lib.scs

Reading file: /eda_disk/pdks/UMC/UMC90nm/Models/Spectre/L90_LL12_V102.mdl.scs

Reading file: /eda_disk/pdks/UMC/UMC90nm/Models/Spectre/L90_LLHVT12_V101.lib.scs

Reading file: /eda_disk/pdks/UMC/UMC90nm/Models/Spectre/L90_LLHVT12_V101.mdl.scs

Reading file: /eda_disk/pdks/UMC/UMC90nm/Models/Spectre/L90_LLLVT12_V102.lib.scs

Reading file: /eda_disk/pdks/UMC/UMC90nm/Models/Spectre/L90_LLLVT12_V102.mdl.scs

Reading file: /eda_disk/pdks/UMC/UMC90nm/Models/Spectre/L90_LLNVT12_V011.lib.scs

Reading file: /eda_disk/pdks/UMC/UMC90nm/Models/Spectre/L90_LLNVT12_V011.mdl.scs

Reading file: /eda_disk/pdks/UMC/UMC90nm/Models/Spectre/L90SP_NCAP10_V112.lib.scs

Reading file: /eda_disk/pdks/UMC/UMC90nm/Models/Spectre/L90SP_NCAP10_V112.mdl.scs

Reading file: /eda_disk/pdks/UMC/UMC90nm/Models/Spectre/L90_NCAP12_LL_V102.lib.scs

Reading file: /eda_disk/pdks/UMC/UMC90nm/Models/Spectre/L90_NCAP12_LL_V102.mdl.scs

Reading file: /eda_disk/pdks/UMC/UMC90nm/Models/Spectre/L90_SP10_V061.lib.scs

Reading file: /eda_disk/pdks/UMC/UMC90nm/Models/Spectre/L90_SP10_V061.mdl.scs

Reading file: /eda_disk/pdks/UMC/UMC90nm/Models/Spectre/L90_SPHVT10_V111.lib.scs

Reading file: /eda_disk/pdks/UMC/UMC90nm/Models/Spectre/L90_SPHVT10_V111.mdl.scs

Reading file: /eda_disk/pdks/UMC/UMC90nm/Models/Spectre/L90_SPLVT10_V102.lib.scs

Reading file: /eda_disk/pdks/UMC/UMC90nm/Models/Spectre/L90_SPLVT10_V102.mdl.scs

Reading file: /eda_disk/pdks/UMC/UMC90nm/Models/Spectre/L90_SPNVT10_V011.lib.scs

Reading file: /eda_disk/pdks/UMC/UMC90nm/Models/Spectre/L90_SPNVT10_V011.mdl.scs

Reading file: /eda_disk/pdks/UMC/UMC90nm/Models/Spectre/L90_mimcaps_20f_kf_V011.lib.scs

Reading file: /eda_disk/pdks/UMC/UMC90nm/Models/Spectre/L90_mimcaps_20f_kf_V011.mdl.scs

Reading file: /eda_disk/pdks/UMC/UMC90nm/Models/Spectre/L90_momcaps_V041.lib.scs

Reading file: /eda_disk/pdks/UMC/UMC90nm/Models/Spectre/L90_momcaps_V041.mdl.scs

Reading file: /eda_disk/pdks/UMC/UMC90nm/Models/Spectre/L90_vardiop_rf_v011.lib.scs

Reading file: /eda_disk/pdks/UMC/UMC90nm/Models/Spectre/L90_vardiop_rf_v011.mdl.scs

Reading file: /eda_disk/pdks/UMC/UMC90nm/Models/Spectre/L90_varmis_12_llrf_V021.lib.scs

Reading file: /eda_disk/pdks/UMC/UMC90nm/Models/Spectre/L90_varmis_12_llrf_V021.mdl.scs

Reading file: /eda_disk/pdks/UMC/UMC90nm/Models/Spectre/momcaps_array_vp3_rfvcl_V011.lib.scs

Reading file: /eda_disk/pdks/UMC/UMC90nm/Models/Spectre/momcaps_array_vp3_rfvcl_V011.typ.scs

Reading file: /eda_disk/pdks/UMC/UMC90nm/Models/Spectre/momcaps_array_vp4_rfvcl_V011.lib.scs

Reading file: /eda_disk/pdks/UMC/UMC90nm/Models/Spectre/momcaps_array_vp4_rfvcl_V011.typ.scs

Reading file: /eda_disk/pdks/UMC/UMC90nm/Models/Spectre/rnhr_rf_V011.lib.scs

Reading file: /eda_disk/pdks/UMC/UMC90nm/Models/Spectre/rnhr_rf_V011.mdl.scs

Reading file: /eda_disk/pdks/UMC/UMC90nm/Models/Spectre/res_poly.va

Reading file: /eda_disk/pdks/UMC/UMC90nm/Models/Spectre/rnnpo_rf_V011.lib.scs

Reading file: /eda_disk/pdks/UMC/UMC90nm/Models/Spectre/rnnpo_rf_V011.mdl.scs

Reading file: /eda_disk/pdks/UMC/UMC90nm/Models/Spectre/rnppo_rf_V011.lib.scs

Reading file: /eda_disk/pdks/UMC/UMC90nm/Models/Spectre/rnppo_rf_V011.mdl.scs

Reading file: /eda_disk/pdks/UMC/UMC90nm/Models/Spectre/L90_varmis_10_sprf_V011.lib.scs

Reading file: /eda_disk/pdks/UMC/UMC90nm/Models/Spectre/L90_varmis_10_sprf_V011.mdl.scs

Reading file: /eda_disk/pdks/UMC/UMC90nm/Models/Spectre/bond_pad_v011.lib.scs

Reading file: /eda_disk/pdks/UMC/UMC90nm/Models/Spectre/bond_pad_v011.mdl.scs

Reading file: /eda_disk/pdks/UMC/UMC90nm/Models/Spectre/L90_SP10_RF_V021.lib.scs

Reading file: /eda_disk/pdks/UMC/UMC90nm/Models/Spectre/L90_SP10_RF_V021.mdl.scs

Time for NDB Parsing: CPU = 242.963 ms, elapsed = 6.17778 s.

Time accumulated: CPU = 314.951 ms, elapsed = 6.17779 s.

Peak resident memory used = 45.5 Mbytes.

The CPU load for active processors is :

Spectre 0 (21.3 %) 1 (9.5 %) 2 (5.7 %) 3 (3.8 %)

4 (12.6 %) 5 (7.2 %) 6 (22.1 %) 7 (3.4 %)

Other

Warning from spectre during circuit read-in.

WARNING (SFE-2654): VerilogA module `respoly_va' override primitive/(verilogA module) `respoly_va'.

WARNING (SFE-2654): VerilogA module `respoly_va' override primitive/(verilogA module) `respoly_va'.

Warning from spectre during hierarchy flattening.

WARNING (SFE-1131): Duplicate scope option `tnom' with scope `TopCircuit'. (using last value specified).

Time for Elaboration: CPU = 56.991 ms, elapsed = 76.3879 ms.

Time accumulated: CPU = 372.942 ms, elapsed = 6.2545 s.

Peak resident memory used = 53.6 Mbytes.

Notice from spectre during hierarchy flattening.

Nport compression is disabled on instance I15 because its port number 2 is smaller than 10.

Nport compression is disabled on instance I16 because its port number 2 is smaller than 10.

Time for EDB Visiting: CPU = 2 ms, elapsed = 2.0771 ms.

Time accumulated: CPU = 375.942 ms, elapsed = 6.25691 s.

Peak resident memory used = 54.5 Mbytes.

Reading file: /projects/VLSI_labs/inductor4/mommdl/text.txt

Notice from spectre during initial setup.

S parameters are passive in file `/projects/VLSI_labs/inductor4/mommdl/text.txt'.

S parameters are passive in file `/projects/VLSI_labs/RFIC/inductor4/mommdl/text.txt'.

Global user options:

reltol = 0.001

vabstol = 1e-06

iabstol = 1e-12

temp = 27

gmin = 1e-12

rforce = 1

maxnotes = 5

maxwarns = 5

digits = 5

cols = 80

pivrel = 0.001

sensfile = ../psf/sens.output

checklimitdest = psf

save = allpub

tnom = 25

tnom = 27

scalem = 1

scale = 1

Scoped user options:

Circuit inventory:

nodes 23

bsim4 5

capacitor 35

diode 2

inductor 4

nport 2

resistor 16

vsource 4

Analysis and control statement inventory:

hb 1

hbnoise 1

info 6

Output statements:

.probe 0

.measure 0

save 0

Time for parsing: CPU = 18.997 ms, elapsed = 1.64109 s.

Time accumulated: CPU = 394.939 ms, elapsed = 7.89827 s.

Peak resident memory used = 57.1 Mbytes.

~~~~~~~~~~~~~~~~~~~~~~

Pre-Simulation Summary

~~~~~~~~~~~~~~~~~~~~~~

~~~~~~~~~~~~~~~~~~~~~~

Entering remote command mode using MPSC service (spectre, ipi, v0.0, spectre0_21767_1, ).

Warning from spectre.

WARNING (SPECTRE-16707): Only tran supports psfxl format, result of other analyses will be in psfbin format.

Error found by spectre during periodic steady state analysis `hb'.

ERROR (CMI-2208): `V3' is a periodic input signal, which is inconsistent with autonomous circuits.

Analysis `hb' was terminated prematurely due to an error.

Error found by spectre.

ERROR (SPCRTRF-15225): The hbnoise analysis was skipped because a HB analysis must be run first.

Analysis `hbnoise' was terminated prematurely due to an error.

modelParameter: writing model parameter values to rawfile.

Opening the PSF file ../psf/modelParameter.info ...

element: writing instance parameter values to rawfile.

Opening the PSF file ../psf/element.info ...

outputParameter: writing output parameter values to rawfile.

Opening the PSF file ../psf/outputParameter.info ...

designParamVals: writing netlist parameters to rawfile.

Opening the PSFASCII file ../psf/designParamVals.info ...

primitives: writing primitives to rawfile.

Opening the PSFASCII file ../psf/primitives.info.primitives ...

subckts: writing subcircuits to rawfile.

Opening the PSFASCII file ../psf/subckts.info.subckts ...

Difference in power values after performing a PSS analysis

Hello

I am running a PSS analysis for my RF rectifier. I am trying to get the power plot of the input source "port" by selecting Direct plot-power. However, the plot varies if select "instance with 2 terminals" and a "fixed R port".

Why is it so? Which value should I consider.?

?

fundamental frequency problem in HB

Hello, i have tried to simulate a mixer with LO=303ps=3.3GHz Vpulse RF=6.6GHz VSIN as shown bellow.

and i defined HB to see the combinations of these tones, but it says "The source V6 couldn't find matched freq"

The HB definition , the error and the full the attached full LOG are shown bellow.

Where did i go wrong?

Thanks

community.cadence.com/.../8508.log.txt

common source amplifier of RF signal problem

Hello,my input signal is 3GHz and 0.3V i need my signal to be at least 0.7,so i built a common source amplifier by the principle of the schematics bellow.

as you can see,from my operating point simulation i have gm=10.48m my Rd=1K from the formula bellow A=gmRd ,so it needs to amplify my signal 10 times.

instead the signal is decreased as shown in the transient plot bellow.where did i go wrong?

maybe it's the output port putting impedance that i am not aware of?

Thanks

HB simulation of a mixer using two different oscilator sources

Hello , I am trying to simulate a 6.66GHz 3.3GHz mixer where oscillators act as sources.

I have tested oscillator 6.66G ,oscillator 3.3G and the mixer with VSIN sources separately in a different schematics as shown bellow and the works fine.

After that i converted them into symbols and tried to put the 3.3G oscillator and the 6.66G oscillator and the mixer(connected to VSIN 6.66GHz 3.3GGHz) on the same schematics , as shown bellow.

A transient simulation shown good simultaneous results that all three components are working , as shown in the plot near the end,but i tried to run two tone HB 1/303.03p 6.6Ghz simulation with the "oscillator option" turned off(because there are two different oscillators so we need 4 nets to be defined in HB).

The HB shows me a good harmonics on the mixer but the two oscillators set apart are not functioning in contradiction with TRANSIENT as you can see in the end.

so how could we make HB recognize the functionality of all 3 components together ?(those oscillators need to replace the VSIN components in the mixer)

i have added the full simulation log in the end.

Thanks

community.cadence.com/.../sim_5F00_log.txt

HB and TRANSIENT shows different result regarding dc block

Hello, i implemented a DC block of 100pf to remove the DC component on the LO_not net, as shown bellow.

When i checked with HB then it shows that the DC component was removed( the plots of before DC block net and after DC block net shown bellow)

but when i tested both nets on Transient then i see that the LO_not net keeps oscilating around the same DC.

the full log of the simulation was attached,where did i go wrong?

Thanks

community.cadence.com/.../2500.log.txt

Constant Q Circles in Smith Chart

Dear all,

I apologize in advance if this question has been asked previously (I was unable to find it), but is there a way to plot constant Q circles in Virtuoso's Smith Chart? By constant Q circles I am referring to the locus of points were X/R is constant. (reactance/resistance)

Thanks

Improve the Insertion loss of a 1st order Polyphase filter

I am designing a Polyphase filter as the main block for my Quadrature phase generator.

I am using the 1st order polyphase filter to check how much insertion loss can be expected before I fix the design. After the SP analysis I got an insertion loss of(S21 = 7.6dB)

I have attached the circuit I used and the testbench. What can do to improve my testbench to get a lower insertion loss (~ 4dB)?

operating point data contradicts region data

Hello, i am trying to bias my mixer transistors to be in saturation (region 2)

The operating point data shown bellow fits the conditions of saturation, but my transistor region status is 1(linear) as shown in the table bellow.

where did i go wrong?

Thanks

Vd=126m Vg=780m Vs=100m Vth=657m

Vgs=780-100=750m >Vth=657m

Vdg=126m-780m=-654m>-657m

transistor state in Vpulse source

Hello, i am simulation a mixer with LO vpulse and RF with sinus source,

The mixer output spectrum works fine as shown bellow,but when i look and the BIAS state of LO transistor it shows me that its in cutoff region as shown in the table in the end.

i understand the the LO source needs to switch the transistor from cuttoff to saturation, is there a way i can see the states in which the transistors switches?(i am not sure it goes to region 2)

Thanks

LO source

RF source

OUTPUT spectrum

path error connecting mixer to amplifier

Hello , i have built a cascaded amplifier , which i turned it into a symbol and it worked fine as shown bellow.

When i tried to add it to my mixer it gives me a problem shown in the end.

where did i shorted ? its just replacing the ideal VSIN source of the amplifier with the output of the mixer.

The full LOG was attached in the end.

Thanks

community.cadence.com/.../0676.log.txt

VCO verilogA model not running PSS

Dear all,

I have a verilogA model of a VCO implemented as such:

_________________________________________________________________________________

`include "disciplines.vams"

`include "constants.vams"

//

// Voltage controlled oscillator with no jitter

//

module vco1 (out, in);

input in; voltage in; // input terminal

output out; voltage out; // output terminal

parameter real vmin=0; // input voltage that corresponds to minimum output frequency

parameter real vmax=vmin+1 from (vmin:inf); // input voltage that corresponds to maximum output frequency

parameter real fmin=1 from (0:inf); // minimum output frequency

parameter real fmax=2*fmin from (fmin:inf); // maximum output frequency

parameter real tt=0.01/fmax from (0:inf); // output transition time

parameter real ttol=1u/fmax from (0:1/fmax); // time tolerance

parameter real ampl=0.5 from (0:inf);

real freq, phase;

integer n;

analog begin

// compute the freq from the input voltage

freq = (V(in) - vmin)*(fmax - fmin) / (vmax - vmin) + fmin;

// bound the frequency (this is optional)

if (freq > fmax) freq = fmax;

if (freq < fmin) freq = fmin;

// bound the time step to assure no cycles are skipped

$bound_step(0.2/freq);

// phase is the integral of the freq modulo 2pi

phase = 2*`M_PI*idtmod(freq, 0.0, 1.0, -0.5);

// generate the output

V(out) <+ ampl*cos(phase);

end

endmodule

_________________________________________________________________________________

I am trying to run a PSS analysis on a PLL consisting of the above VCO, a real PFD design and a simple 1st order filter made up of analogLib components. While a transient analysis

is able to finish without any issues or warnings a PSS analysis will not converge. Specifically I can see from the transient that the PLL has locked within about 30ns. PSS analysis detects steady state

at 33ns but fails at arround 32ns-33ns. I have simulated the PLL using transient for up to 150ns and it is perfectly stable. I have tried numerous options on the PSS but without getting any results. I have tried to force the

PSS to run a very long transient simulation to ensure the PLL has stabilized but still no luck. I specifically get the following errors:

____________________________________

==============================

`pss': time = (32 ns -> 33 ns)

==============================

Zero diagonal found in Jacobian at `net028' and `net028'.

Zero diagonal found in Jacobian at `net028' and `net028'.

Zero diagonal found in Jacobian at `net028' and `net028'.

Zero diagonal found in Jacobian at `net028' and `net028'.

Jacobian was reordered during integration. Don't use swap file in PSS analysis

Zero diagonal found in Jacobian at `net028' and `net028'.

pss: time = 32.03 ns (2.54 %), step = 441.1 fs (44.1 m%)

pss: time = 32.08 ns (7.56 %), step = 779.7 fs (78 m%)

pss: time = 32.13 ns (12.5 %), step = 846.5 fs (84.6 m%)

pss: time = 32.18 ns (17.6 %), step = 554.7 fs (55.5 m%)

pss: time = 32.23 ns (22.6 %), step = 2.632 ps (263 m%)

pss: time = 32.28 ns (27.6 %), step = 2.632 ps (263 m%)

pss: time = 32.33 ns (32.6 %), step = 2.632 ps (263 m%)

pss: time = 32.38 ns (37.6 %), step = 2.632 ps (263 m%)

pss: time = 32.43 ns (42.5 %), step = 511.1 fs (51.1 m%)

pss: time = 32.48 ns (47.6 %), step = 2.632 ps (263 m%)

pss: time = 32.53 ns (52.5 %), step = 406.3 fs (40.6 m%)

pss: time = 32.58 ns (57.5 %), step = 1.154 ps (115 m%)

pss: time = 32.63 ns (62.5 %), step = 454.9 fs (45.5 m%)

pss: time = 32.68 ns (67.6 %), step = 2.632 ps (263 m%)

pss: time = 32.73 ns (72.6 %), step = 2.632 ps (263 m%)

pss: time = 32.78 ns (77.6 %), step = 2.632 ps (263 m%)

pss: time = 32.83 ns (82.6 %), step = 2.632 ps (263 m%)

pss: time = 32.88 ns (87.5 %), step = 371.3 fs (37.1 m%)

pss: time = 32.93 ns (92.7 %), step = 2.632 ps (263 m%)

pss: time = 32.98 ns (97.7 %), step = 2.632 ps (263 m%)

Conv norm = 14.3e+06, max dV(net024) = 36.5826 kV, took 1.43 s.

==============================

`pss': time = (32 ns -> 33 ns)

==============================

Error found by spectre at time = 32.08 ns during periodic steady state analysis `pss'.

ERROR (SPECTRE-16192): No convergence achieved with the minimum time step specified. Last acceptable solution computed at 32 ns.

The values for those nodes that did not converge on the last Newton iteration are given below. The manner in which the convergence criteria were not satisfied is also given.

Failed test: | Value | > RelTol*Ref + AbsTol

Top 10 Residue too large Convergence failure:

V(I62.I57.I60.net7) = -3.16705 V, previously -3.16705 V.

residue too large: | 39.6793e+114 A | > 396.793e+108 A + 100 fA

V(I62.I58.I80.net7) = -1.5006 V, previously -1.5006 V.

residue too large: | 1.83385e+117 A | > 18.3385e+111 A + 100 fA

V(I62.I58.I60.net7) = -8.61477 V, previously -8.61477 V.

residue too large: | 19.8331e+114 A | > 198.331e+108 A + 100 fA

V(I62.I58.net1) = 1.00293 V, previously 1.00293 V.

residue too large: | -36.036e+24 A | > 360.36e+18 A + 100 fA

V(I62.I58.CLK_i) = 5.58113 V, previously 5.58113 V.

residue too large: | -733.948e+15 A | > 7.33948 TA + 100 fA

V(I62.net020) = -27.3343 V, previously -27.3343 V.

residue too large: | 4.28083e+108 A | > 42.8083e+102 A + 100 fA

V(UP) = -682.489 mV, previously -682.489 mV.

residue too large: | 40.4116e+108 A | > 404.116e+102 A + 100 fA

V(I62.I58.B) = -12.6532 V, previously -12.6532 V.

residue too large: | 74.695e+117 A | > 746.95e+111 A + 100 fA

V(I62.I58.net019) = -11.1717 V, previously -11.1717 V.

residue too large: | 11.3806e+15 A | > 113.806 GA + 100 fA

V(I62.net037) = 384.159 V, previously 384.159 V.

residue too large: | -339.142e+117 A | > 3.39142e+114 A + 100 fA

_______________________________________________________________

Any input is highly appreciated.

Thanks

Verifying PSTB results by using PAC results.

Dear All,

We have successfully verified the STB analysis results by using AC analysis results.

We have injected voltage and the current sources as given in the document https://kenkundert.com/docs/cd2001-01.pdf.

And for each we have found the AC gains. We then used the equations given in pages 35-36 of the above document.

However, for PSTB:- how to use the PAC results to verify the PSTB result is the QUESTION. We are NOT sure which PAC-sideband Spectre is taking ?

Could anybody please tell me how to verify the PSTB results with PAC results.

I have filed a SR Case# 46338720 regarding this. But, it is still hanging over months.

I guess, the AEs may NOT be able to understand the questions or they do NOT find the right person in R&D to clear the doubts.

Kind Regards,

Different simulation result from ADE L and ADE XL

Hello everyone,

I am using cadence ICADV 12.3 and ADE XL for my simulations. For some reason, I am having a differences in the result I get from ADE-L and ADE-XL simulations despite that everything is the same for both of the simulations. Below is the complete description of what I did.

From DC simulation, I was trying to plot the figure of Id versus Vgs while Vgs is swept from 0 to 1.2v. To this end, I included a “Definition File”, which I call “saveop.scs” and it has following command to save the transistor’ operating point information. save MN:all

The expression getData(“MN:id” ?result “dc”) is used to get the id curve. But for some reason I am getting different results from ADE L and ADE XL simulation.I know that there are other ways to do this plot. The reason I used this way is that I also need other small signal parameters (like cgg, cdd, region,…) for my post processing but they also have the same problem. I would appreciate any sort of help in this regard. Thanks in advance.

amplifier Assura LVS check problem

Hello , i have built an aplifier in schematics which worked fine, when i tried to convert my schematics into layout , when i tried Assura LVS check,i get an error as shown bellow.

I have attached the full LOG.

Where did i go wring with the LVS rule file?

Thanks.

community.cadence.com/.../0728.log.txt

PPV extraction through PSS simulation

Recently, I’m studying perturbation projection vector(PPV) based phase noise computation. There are three simulation methods to extract PPV, of which PSS is the fastest and most convenient method. As claimed in the paper titled"A Comparison of Simulation Strategies for Estimating Phase Noise in Oscillators", the PPV vector is automatically calculated during the PSS simulation without any other processing. I found that there is a “save osc ppv” option in spectre PSS simulation, and I can get the node voltage based PPV through result browser(the results seem odd), whose unit is V-1. My problem is how to get current based PPV through PSS simulation just like in the aforementioned paper, whose unit is A-1?

Problem of phase noise file used in vsource/port

Hi,

I want to put the phase noise file into the vsource/port for a PLL phase domain simulation. The phase noise file is from a VCO PSS+Pnoise simulation and is saved as ".in.spectre" format. If the unit in the vsource/port noise parameter setting is V^2/Hz, than the PLL noise simulation works well, but the phase noise value is not correct, which I guess we need to do the calibration (calibrate its amplitude to 0dBm or 1V^2?). If the unit is dBc, there is one error after I set the source type as sine in vsource/port:

ERROR (CMI-2913): N_VCO: At least one frequency in freqvec or in freq and freq2 should be greater than zero for noisetype=ssbphasenoise.

If the noise parameter is set to "Noise/Frequency points" with dBc, the simulation also works well. But I need to manually key all points.

Please advice. My VIrtuoso is 6.1.7-64b.500.6, MMSIM/151.

Thank you.